33+

Years of experience我们在台湾、中国与韩国已累积Tape out服务经验。

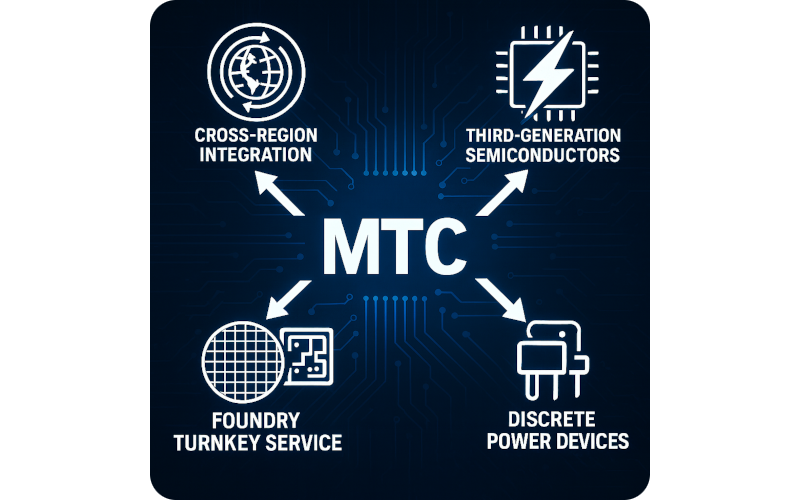

美禄科技同样也有开发自有品牌的电源功率相关应用元件设计、制造与行销,并提供严格品质管理与售后服务客户。

了解更多

Why Choose Us

美禄科技保证将带给客户最好的晶圆代工代理服务, MOSFET与Photo Coupler产品, 而美禄科技期待与您建立长远互惠合作的伙伴关系。

-

专业团队

-

品质管理

-

技术整合

-

客户满意

News & Blog

我们将定期发布美禄科技最新资讯